ブログ:

【三菱ディスプレイ】第2「ApalisモジュールにおけるLVDS」

![]()

この5回にわたるブログ記事連載では、LVDSディスプレイの基礎的な概念について説明します。以前のセッションでは、LCDのタイミングの基礎について学びました。今回は、Apalis iMX8が、LVDS信号を扱う仕組みを説明します。

Linuxのデバイス定義について説明する前に、このディスプレイで使われる信号であるLVDSについてもう少し詳しく説明した方がよいと思われます。

LVDSのインターフェイスの公式名称は、FPD-LinkまたはFlatLinkといい、低電圧差動信号(LVDS)テクノロジーを使います。しかし多くの場合は、このインターフェイスをLVDSと呼んでしまっています。

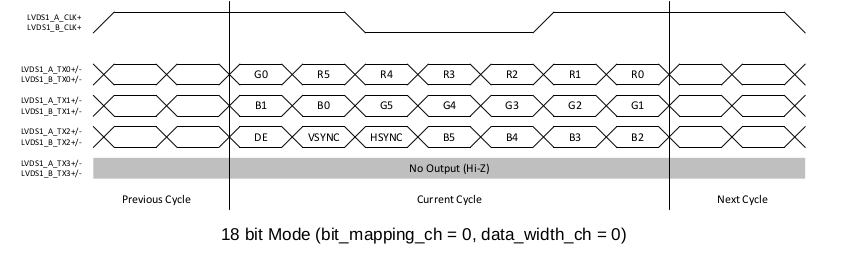

- 制御信号(表示有効、垂直および水平同期)を含む18ビットのRGBインターフェイスには、各FPD_Link/FlatLinkチャネルそれぞれで3組のLVDSデータペアが必要です。

- 24ビットインターフェイス用の追加の色ビットは、LVDSデータペアの4組目にシリアル化されます。

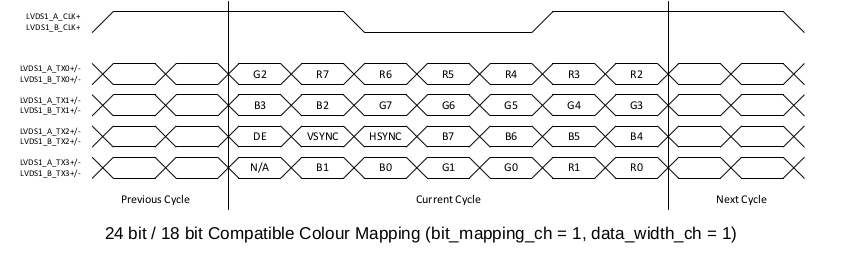

- 24ビットインターフェイスには、2つのカラーマッピング基準があります。あまり用いられない「24ビット互換性」(JEIDA形式)基準では、各色の下位2ビットをLVDSペアの4組目に入れます。この基準は、18ビットモードとの後方互換性があります。18ビットのディスプレイを24ビットのインターフェイスに接続したり、その逆の接続を行うことも可能です。いずれの場合も、最下位ビットが使われるか使われないかの違いになります。

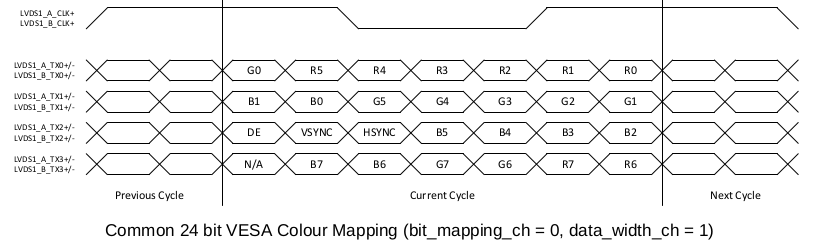

- それよりも頻繁に使用されるのが18/24ビットカラーマッピング基準(SPWGまたは別名VESA形式)です。この基準では、各色の上位2ビットをLVDSペアの4組目にシリアル化します。このモードでは、後方互換性がありません。

Apalis iMX8とiMX6双方のLVDSインターフェイスは、異なるカラーマッピングと深度に対応するよう設定が可能です。これにより、18ビットおよび24ビットのディスプレイ、さらに双方のカラーマッピングとの互換性を確保します。カラーマッピングはデバイス定義で選択することもできます。

上の図は、「24ビット互換性カラーマッピング」(JEIDA形式)のLVDS出力信号を示しています。RGBビットの名前は、「24ビットRGB」の列にある色の名前に対応しています。このモードを有効にするには、LDB Control Register(LDB_CTRL)のbit_mapping_chフィールドを1(JEIDA基準)に設定し、data_width_chフィールドを1(24ビット)に設定します。ただし、これは、デバイス定義で適切な設定を行えばすでに設定が終わっているはずです(後ほど説明します)。

次の図は、よく利用される24ビットカラーマッピング(VESA形式)のLVDS出力信号を示しています。RGBビットの名前は、「24ビットRGB」の列にある色の名前に対応しています。このモードを有効にするには、LDB Control Register(LDB_CTRL)のbit_mapping_chフィールドを0に設定し、data_width_chフィールドを1(24ビット)に設定します。この設定についても、上記同様、デバイス定義で実行可能です。

上の図は、18ビットインターフェイスのLVDS出力信号を示しています。RGBビットの名前は、「18ビットRGB」の列にある色の名前に対応しています。このモードを有効にするには、LDB Control Register(LDB_CTRL)のbit_mapping_chフィールドを0(SPWG基準)に設定し、data_width_chフィールドを0(18ビット)に設定します。この設定についても、上記同様、デバイス定義で実行可能です。

さらに、LVDSディスプレイを実装する前に、カラーマッピングについてはっきりさせておくべき重要な点があります。選択したシステムで利用可能なチャネルと必要な解像度に関する点です。

シングルチャネルLVDSインターフェイスで対応できる解像度は最大1366x768ピクセル、60フレーム毎秒(最大85MHzのピクセルクロック周波数)です。高い解像度を得るにはLVDSチャネルがもう1つ必要となります。

デュアルチャネル構成の場合、奇数のビットを1つ目のチャネルで送信し、偶数のビットを2つ目のチャネルで送信します。デュアルチャネルLVDSインターフェイスで対応できる解像度は最大1920x1200、60フレーム毎秒(最大170MHzのピクセルクロック周波数)です。

シングルチャネルおよびデュアルチャネルモードは、Apalis T30など他のApalisモジュールとの互換性があります。さらに、Apalis iMX6は、2つのシングルチャネルLVDSディスプレイとインターフェイスできます。ディスプレイは、クローンされたコンテンツを表示することも、または、(統合)画像処理ユニットと呼ばれるSoCの内部グラフィックスハードウェア、IPUから独立して稼働させることもできます。ソフトウェアに関しては、すべてToradexがすでに準備をしてあります。必要なOpenGLやW11/WaylandドライバはすでにToradexのBSPに加えられているため、ソフトウェアをToradexのBSPベースにする場合はこれらをシステムに追加する必要はありません。

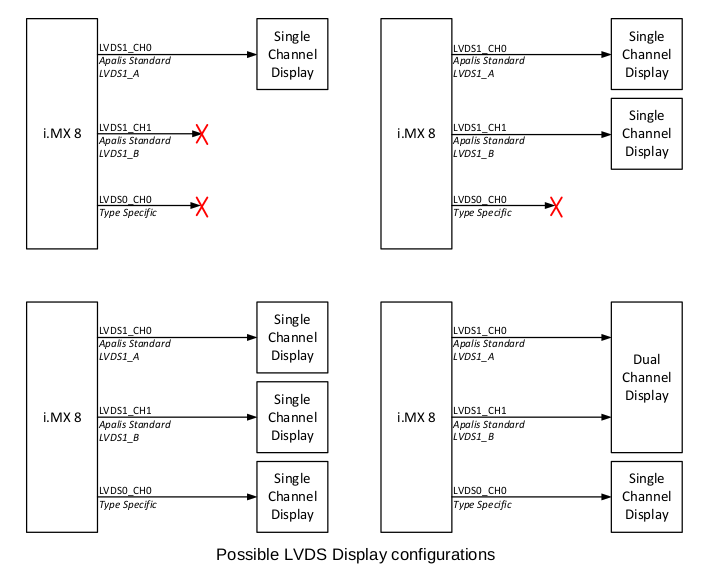

i.MX 8は、デュアルチャネルLVDSポートを2つ(LVDS0とLVDS1)搭載しており、各iMX 8 LVDSポートはそれぞれ最大1080p60まで出力できます。各LVDSポートを2つのシングルチャネルポートに分割することも可能です。

Apalis iMX8では、Apalis標準ピン上でLVDS1ポートがデュアルチャネルLVDSとして搭載されており、他のApalisモジュールとの後方互換性またはアップデートを簡単に実現できます。

Apalisとの互換性があるこのデュアルチャネルに加え、Apalis iMX8モジュールにはもう1つのシングルチャネルLVDSポート(LVDS0)が搭載されています。つまりこれらを総合すると、Apalis iMX8は、最大で3つのシングルチャネルLVDSポート、または、1つのデュアルチャネルLVDSと1つのシングルチャネルを提供することになります。

次の図は、可能なLVDSディスプレイ構成を示しています。LVDS1_CH0とLVDS0_CH0インターフェイスを使用して2つのシングルチャネルディスプレイに接続することは可能ですが、代わりにLVDS1_CH0とLVDS1_CH1の利用を推奨します。

そうすることで、他のApalisモジュールと互換性のある設計になります。LVDS0_CH0は、モジュールエッジコネクタのこのタイプに特有なエリアにあり、ApalisファミリーすべてにおいてこれらのピンがLVDS用に確保されているわけではないためです。

Apalisファミリー全体で互換性のあるシステムの構築をご希望の場合は、Apalis iMX6 LVDS デュアルチャネルインターフェイスとApalis iMX8 LVDS1の双方が同一のピンアウトであることを覚えておくと便利です。

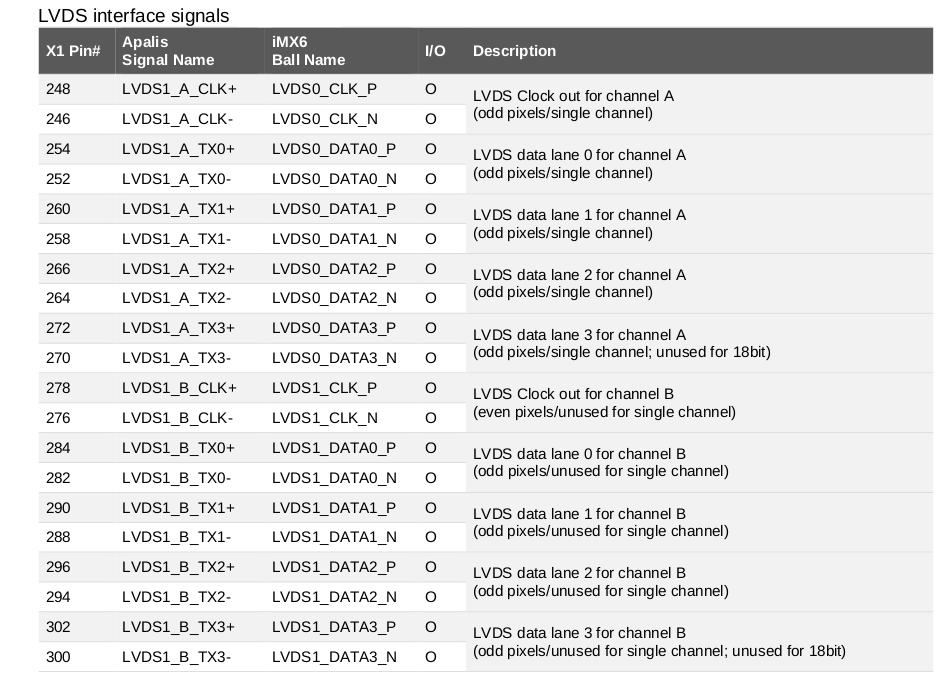

Apalis のLVDSタイプ特有のピン(Apalis iMX6データシートより)

今回の記事では、Apalis iMX8が、LVDS信号を扱う仕組みを説明しました。次回は、Linux Device Treeでこのディスプレイを設定する方法について見ていきます。この記事についてご質問などがありましたら、Toradexのコミュニティに投稿、あるいはToradexの担当者までご連絡ください。