Blog:

Testes de conformidade de Ethernet na Toradex

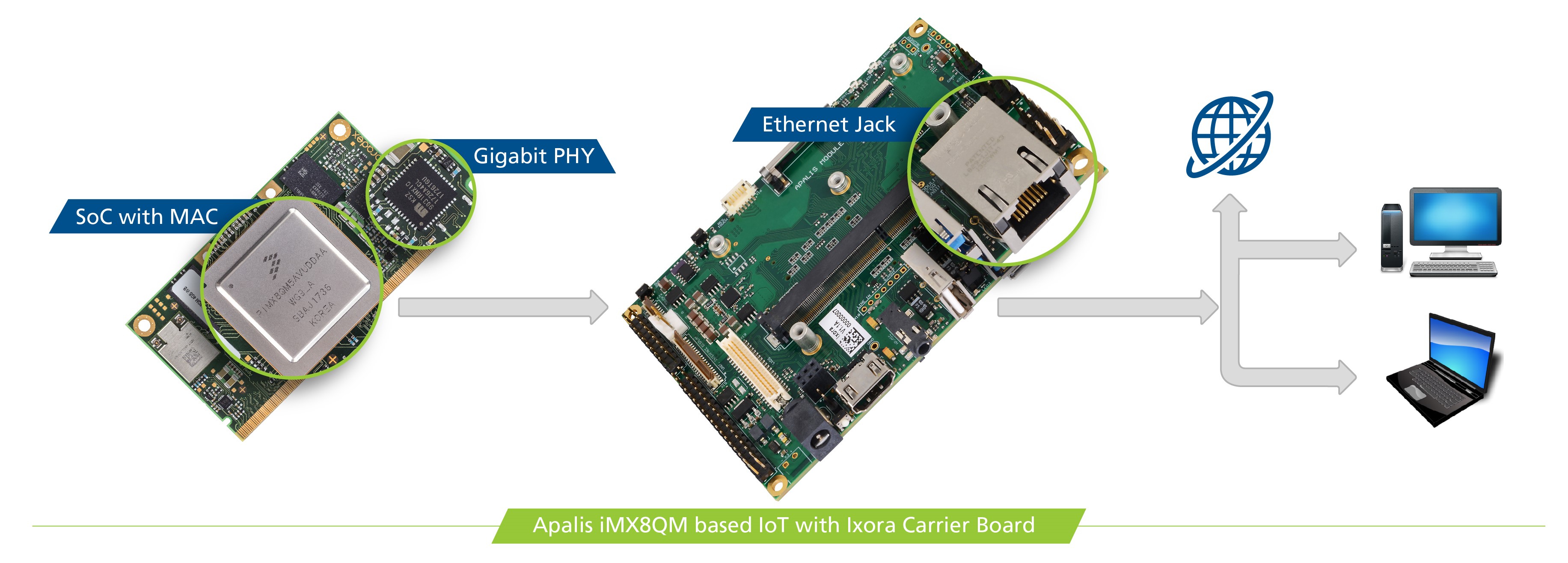

A Toradex oferece sistemas embarcados robustos e confiáveis, que precisam trabalhar continuamente em ambientes extremos. A Ethernet é uma das interfaces mais importantes para a Internet das Coisas (IoT). Neste post, revisaremos alguns padrões de Ethernet e mostraremos como a Toradex realiza seus testes de conformidade.

Após olharmos os padrões, descreveremos nossa configuração de teste, nossos procedimentos eresultados. Um SoM Colibri iMX6ULL e uma Iris Carrier Board foram usados neste exemplo, mas vocêpode usar os procedimentos aqui descritos como modelo para testar placas base customizadas se este tipo de teste fizer parte do seu processo de verificação.

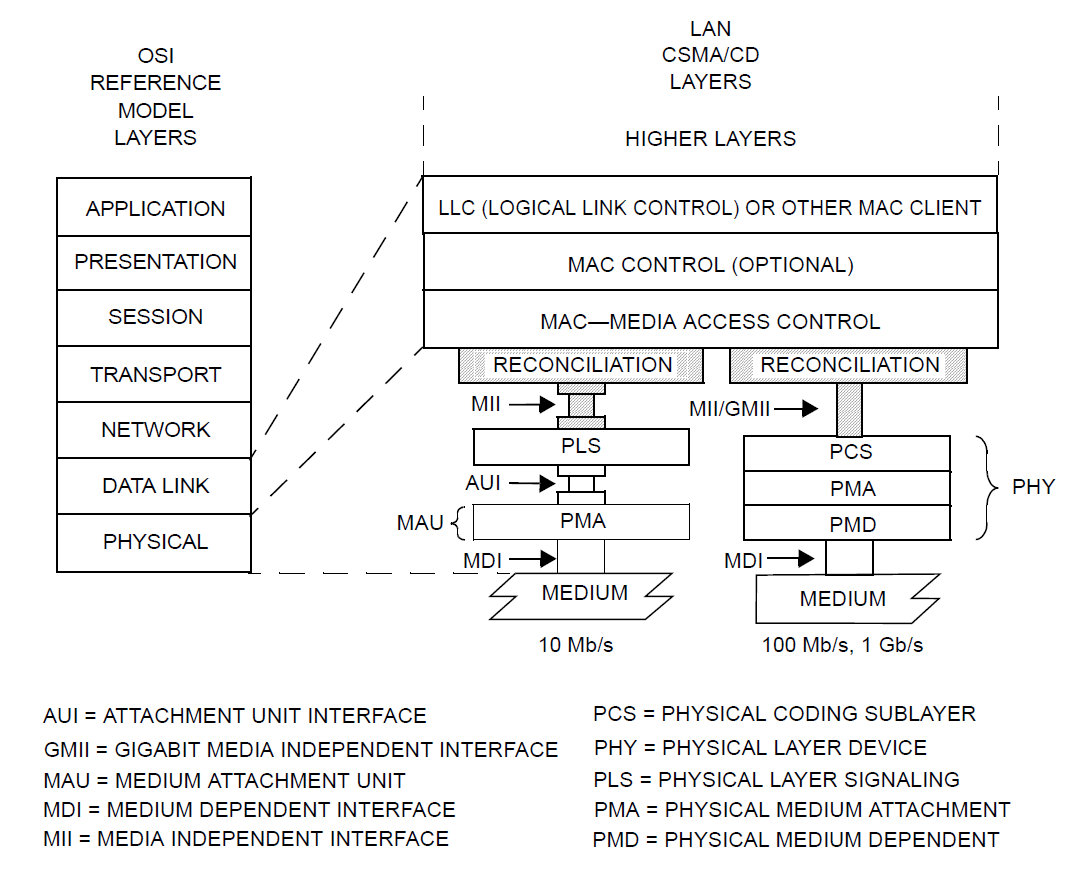

Projetos de Ethernet aderem ao padrão IEEE 802.3, que definem as camadas Física e de Dados do modelo OSI (Open Systems Interconnection) de sete camadas. As características dasformas de onda são todasespecificadas no IEEE 802.3. Durante o projeto,é importante levar este padrão em conta para permitir a compatibilidade e interoperabilidade com outros dispositivos em todos os tipos de ambiente em qualquer lugar do mundo. Caso contrário, é muito provável que ocorram problemas de transmissão e perdas de dados. Testes de conformidade garantem que a implementação cumprao padrão.

Além das características de formas de onda especificadas no padrão IEEE 802.3, o Laboratório de InterOperabilidade da Universidade de New Hampshire (UNH-IOL) fornece procedimentos de teste padrãopara esses sinais. Estes documentos podem ser acessados pelos seguintes links:

OdocumentodopadrãoEthernettemmilharesdepáginas,entãocobriremosaquiapenasosconceitosmaisimportantesealgumasterminologiaschave.

Vamos começar com o meio físico. Os sinais geralmente chegam através de um par trançado de cabos de cobre até um jack Ethernet com a parte magnética integrada na nossa Placa Base, e então continua através de trilhas diferenciais com impedância casada na placa de circuito impresso até o circuito integrado do PHY da Ethernet. Esse dispositivo converte os sinais analógicos do meio para sinais digitais para o processador e vice versa.

Os sinais elétricos primeiramente encontram a Interface Dependente do Meio (MDI - Medium Dependent Interface) do PHY, uma parte da camada física. Diferentes meios físicos têm diferentes características. De acordo com o tipo específico do meio, esses sinais são transformados e enviados para a próxima camada do modelo OSI, a camada de Ligação de Dados (Data Link). Nós fornecemos 10Base-T e 100Base-TX (Fast Ethernet) nos nossos módulos Colibri e 1000Base-T (Gigabit) nos módulos Apalis. A interface padronizada entre as duas primeiras camadas OSI é chamada de Interface Independente do Meio (MII - Media Independent Interface) e é independente da camada física.

|

MII |

Media Independent Interface(Interface Independente do Meio) |

|

RMII |

Reduced Media Independent Interface(Interface Independente do Meio Reduzida) |

|

GMII |

Gigabit Media Independent Interface(Interface Gigabit Independente do Meio) |

|

RGMII |

Reduced Gigabit Media Independent Interface(Interface GigabitIndependente do Meio Reduzida) |

|

SGMII |

Serial Gigabit Media Independent Interface(Interface Serial GigabitIndependente do Meio) |

|

QSGMII |

Quad Serial Gigabit Media Independent Interface(Interface Quad Serial Gigabit Independente do Meio) |

|

XGMII |

10 Gigabit Media Independent Interface(Interface 10 Gigabit Independente do Meio) |

Hoje em dia,já é comum usarmosa mais avançada e retrocompatível Interface Gigabit Independente do Meio Reduzida (RGMII - Reduced Gigabit Media Independent Interface), sendo que a próxima interface para 10 Gigabit já tem o nome de XGMII.

“Reduzida” quer dizer que há menos sinais necessários para implementar o mesmo padrão. Todas as xMII são barramentos de dados paralelos. Há um barramento serial suplementar para fins de gerenciamento chamado Entrada/Saída de Gerenciamento de Dados (MDIO - Management Data Input/Output). A interface xMII termina na camada de Controle de Acesso de Mídia (MAC - Media Access Control). Aqui o já conhecido endereço MAC é usado como um identificador único. A camada MAC pode ser integrada diretamente no Sistema em Chip (SoC), como nos processadores daNXP®,mas também pode estar embutida no mesmo CI do PHY, que é mais conhecido como Controlador Ethernet. O CI Controlador Ethernet, por sua vez, está conectado ao SoC através de uma interface separada como USB ou PCIe. Note que aqui não estamos lidando com as camadas mais altas da OSI e protocolos como ARP, NDP, IP, TCP, UDP, etc., que são organizados em frames e pacotes, já que, para todos esses protocolos, as características elétricas nas primeiras camadas físicas são as mesmas!

Por hora, voltemos à camada física. Há duas principais características da ligação física sobre as quais gostaria de discorrer: velocidade e modo duplex. Nossos módulos suportam velocidades de até1Gbit nos Módulos Apalis e100Mbit nos Módulos Colibri, e ambos os modos half e full duplex. No modo de operação full duplex, os PHYs em ambas as pontas da ligação podem comunicar um com o outro simultaneamente. No modo half duplex, onde o PHY não pode receber e transmitir dados aos mesmo tempo, há necessidade de usar o Acesso Múltiplo com Verificação de Portadora com Detecção de Colisão (CSMA/CD -Carrier Sense Multiple Access with Collision Detection) para evitar colisões e controlar o fluxo de dados.

Como já descrito, os nossos módulos Apalis suportam Gigabit Ethernet. Mas como os dispositivos que estão comunicandosaberão com que velocidade podem mandar os dados? Existe um procedimento de auto-negociação, onde os parceiros configuram a melhor conexão através de pulsos de conexão de 16ms. Deve-se ter cuidado com as configurações de auto-negociação, já que existe um conhecido problema de descasamento duplex, quando os parceiros de conexão estão configurados de maneira fixa. Na parte elétrica da camada física, 10Base-T e 100Base-TX usam dois pares trançados, enquanto1000Base-TX usa quatro. 100Base-TX é mais rápido que 10Base-T, baseado numafrequência muito maior - de 62,5MHz em vez de 10MHz - além de um esquema de modulação de sinal mais denso (PAM-3). A 1000Base-TX usa a mesma frequência que a 100Base-TX, mas transmite através de 4 pares trançados e com um nível maior de modulação (PAM-5). Finalmente, há uma funcionalidade adicional chamada EEE - Ethernet Energeticamente Eficiente. O objetivo deste padrão é economizar energia.

- https://en.wikipedia.org/wiki/Duplex_mismatch

- https://en.wikipedia.org/wiki/Media-independent_interface

- https://www.asix.com.tw/new_alias.php?alias=93&full=http://www.embedded.com/design/202804534

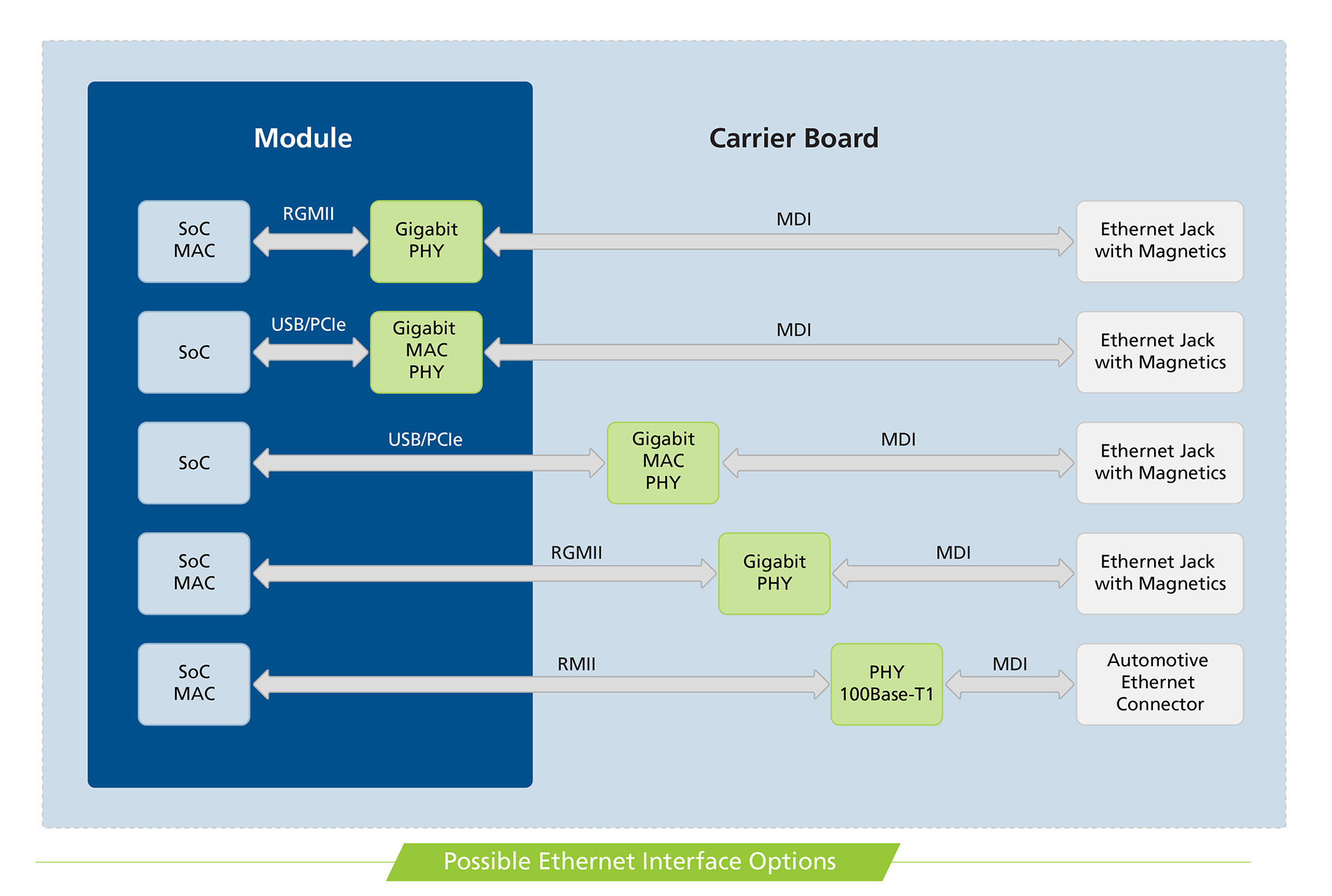

A figura abaixo sumariza as possibilidades de conexão Ethernet nos SoMs Toradex:

Antes de prosseguirmos com os Testes de Conformidade, gostaria de comentar que recebemos várias perguntas sobre 100Base-T1, também conhecida como Ethernet Automotiva. Os clientes querem saber se é possível conectar Ethernet Automotiva a um PHY de Fast Ethernet. A 100Base-T1 tem uma especificação de camada física diferente para cumprir os requisitos de um ambiente exigente como o automotivo. Não é possível conectá-los diretamente, mas o MII ainda é o mesmo! A solução é conectar o PHY 100Base-T1 diretamente à Interface Independente do Meio (MII) do SoC. Consequentemente, você precisará escolher um módulo que tenha os sinais xMII disponíveis no conector da placa! É claro, também, que você terá que projetar sua própria placa base customizada com um PHY 100Base-T1. Aqui você pode encontrar uma lista de módulos da Toradex que fornecem uma xMII no conector do módulo. Note que esta não é uma interface padrão da Toradex e as atribuições de pino variam a cada módulo.

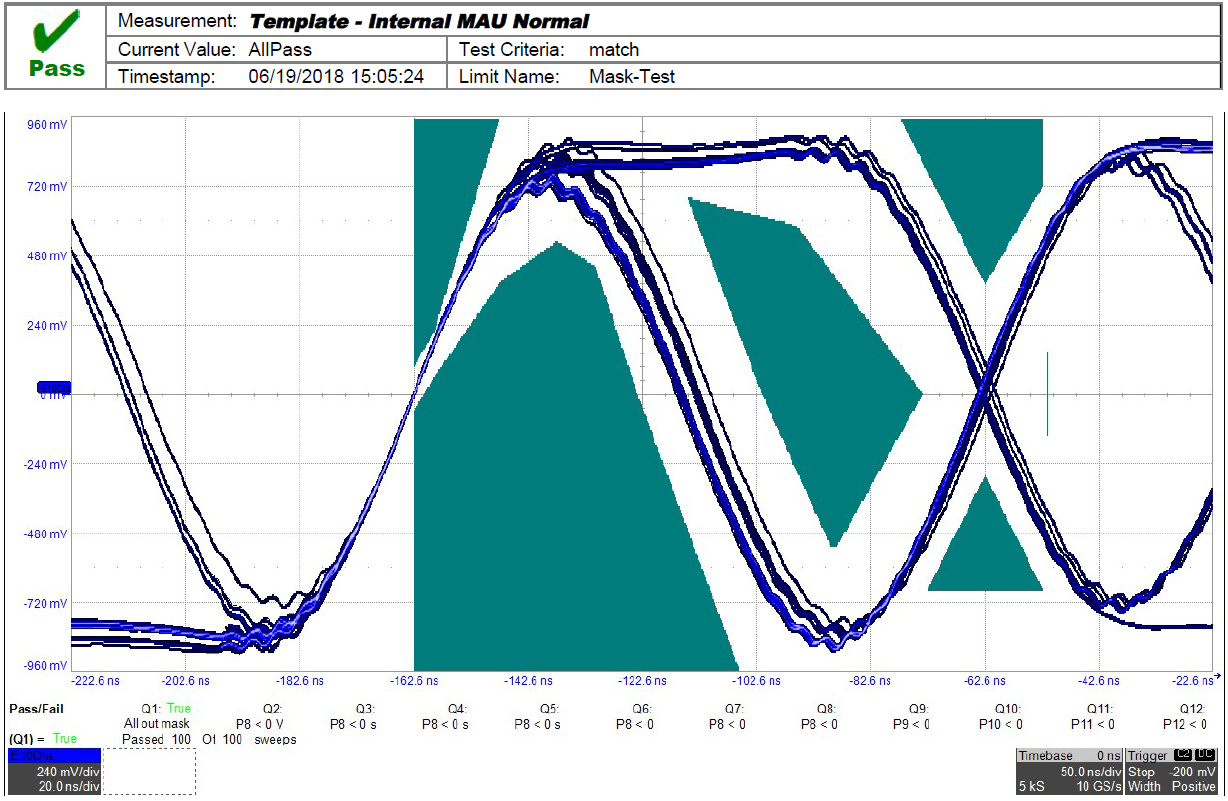

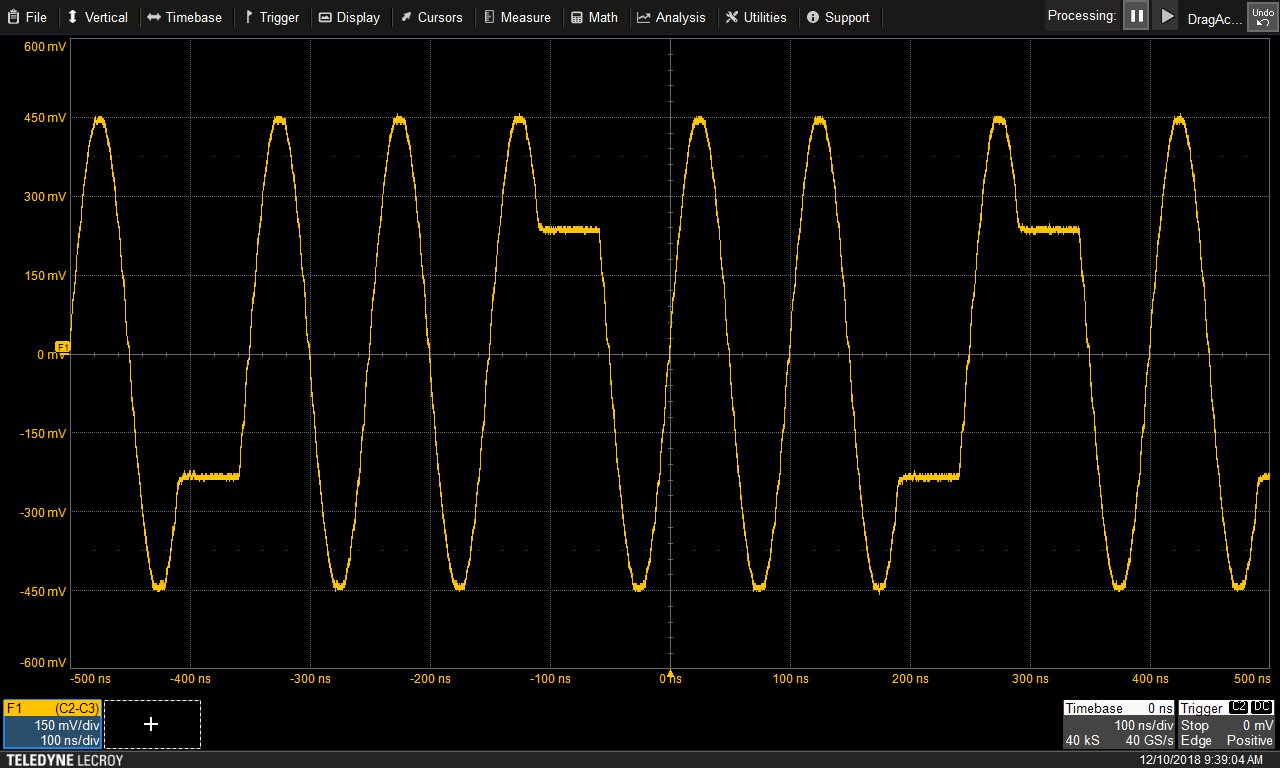

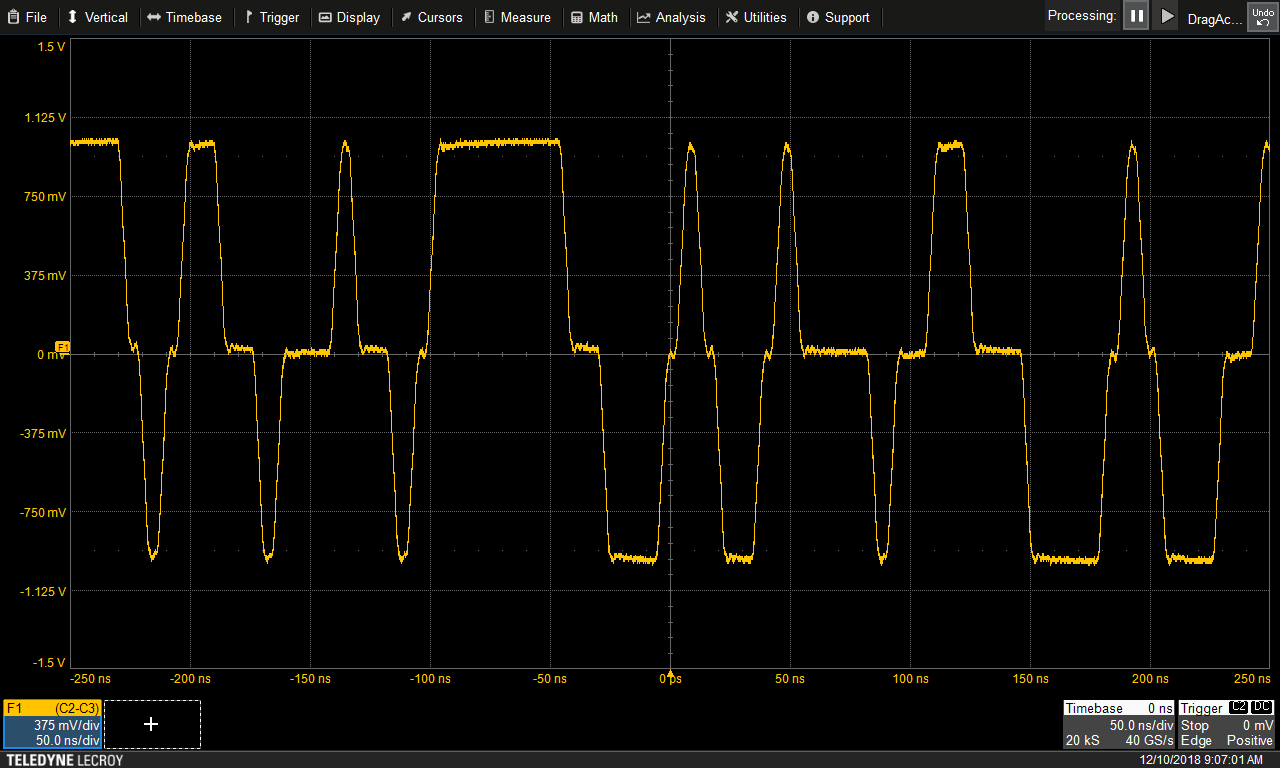

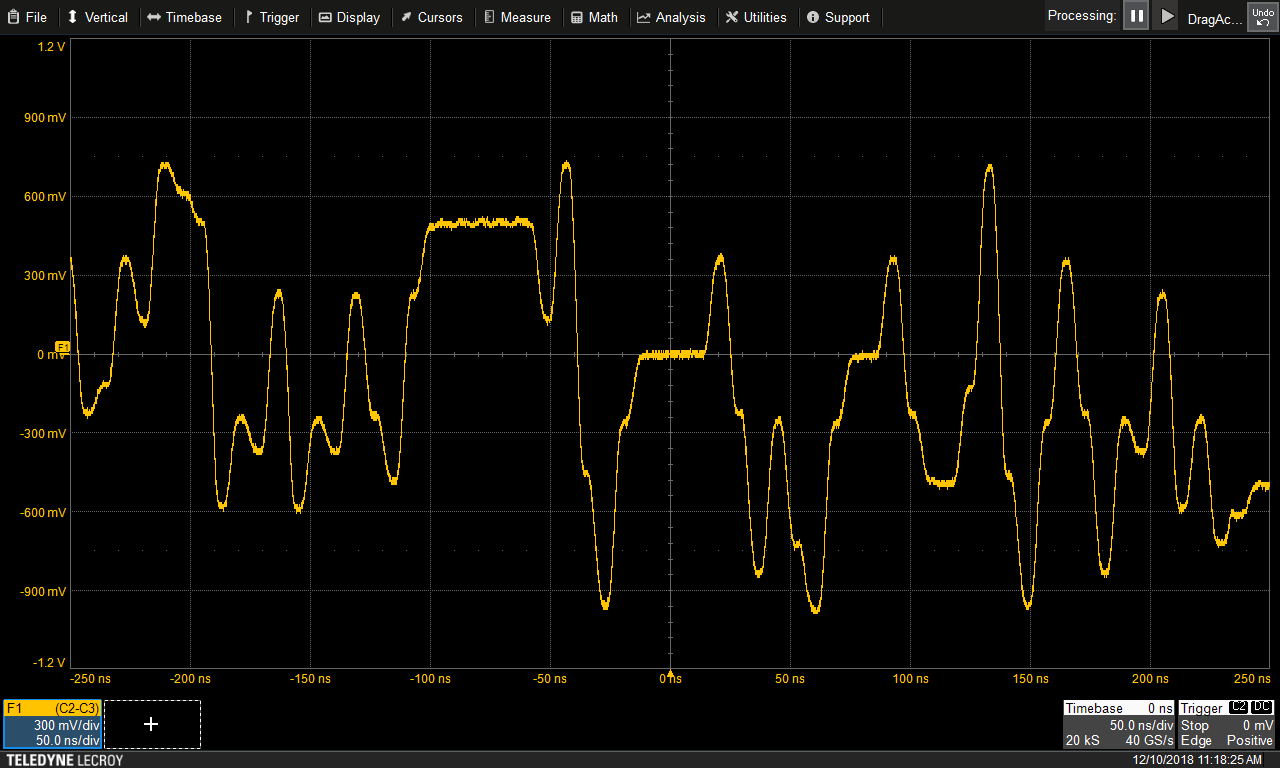

Após esta breve visão geral, continuemos com os testes de conformidade, onde testaremos os sinais elétricos com relação a tempo e tensão. Estes sinais elétricos são totalmente diferentes para 10/100/1000 Mbps e têm diferentes requisitos, como pode ser visto nos oscilogramas.

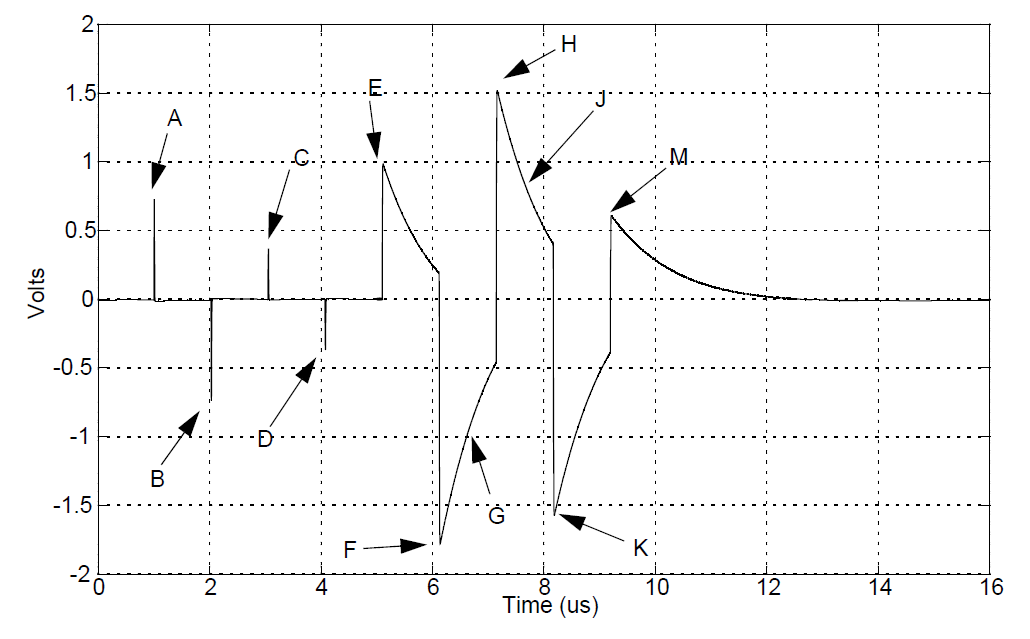

Os testes avaliam as amplitudes das tensões, valores de jitter, tempos de descida/subida e outras características dos sinais. Para cada teste, um sinal de teste definido deve ser gerado pelo dispositivo sob teste (DUT) - por exemplo, um sinal pseudo aleatório contínuo. A forma mais fácil de testar os requisitos de sinal é definir uma máscara de teste. Para cumprir a especificação, os sinais não podem cruzar com a máscara. Os testes de 10Base-T frequentemente são definidos através de uma máscara de teste como visto na primeira figura. Destaco alguns valores: o pico da Tensão Diferencial de Saída (DOV) deve estar entre 2,2V e 2,8V. Os harmônicos da Tensão Diferencial de Saída devem ser maiores que 27dB e todos os valores de jitter devem ser menores que 22ns. O modelo de par trançado para 10Base-T usado em alguns testes de conformidade é particularmente interessante. Com um circuito equivalente baseado em elementos aglomerados, é possível modelar múltiplos elementos de transmissão diferentes usando somente componentes passivos. Dependendo do PHY, é preciso estabelecer um parceiro de ligação para os testes de conformidade 10Base-T. Você pode baixar o Relatório de Teste do Colibri iMX6ULL como exemplo e encontrar todos os testes.

As características da interface para 100Base-TX são definidas na tablea 2 baseadas nos sinais de tensão MLT-3 com três níveis. Os dados são pré-codificados com o algoritmo 4B5B, então é possível recuperar o clock a partir do fluxo de dados, já que se força uma transição de nível. Para nosso equipamento de teste, um padrão de teste pseudo aleatório (PRBS7) é suficiente para todos os testes. Todavia, alguns testes somente serão acionados em padrões definidos, com medições naquele momento e com valores específicos.

|

Características |

Min |

Max |

Unidade |

|

UTP DOV Base a Superior/Inferior |

950 |

1050 |

mV |

|

Simetria da Amplitude do Sinal |

98 |

102 |

% |

|

Tempo Subida/Descida |

3 |

5 |

ns |

|

Simetria do Tempo de Subida/Descida |

0 |

500 |

ps |

|

Distorção de Ciclo de Trabalho |

-250 |

250 |

ps |

|

Jitter de Transmissão |

0 |

1.4 |

ns |

|

Overshoot |

0 |

5 |

% |

Os critérios de teste são definidos de forma similar para a 1000Base-T, que não listarei aqui. Para estes testes, um perturbador adicional, na forma de um Gerador de Onda Arbitrária (AWG) é necessário para criar os sinais de perturbação necessários com frequências de 31,25 MHz e 20,833 MHz. Na figura 5 você pode ver o padrão de teste do modo de teste 1 produzido pelo PHY. Há quatro diferentes padrões de testes que podem ser geradores através da configuração do registrador MDIO do PHY. Não se esqueça que os testes de conformidade devem ser realizados quatro vezes por causa dos quatro pares trançados.

Já vimos alguns dos requisitos elétricos que devem ser cumpridos para conformidade com a interface. Antes de olharmos com mais detalhes para os equipamentos de teste, quero tentar resolver a questão mais importante deste blog: Como gerar estes sinais de teste?

Cada fabricante de PHY tem um método customizado para modificar o registro necessário para entrar no modo de teste. Geralmente essa informação não é pública e é preciso perguntar ao fabricante do seu PHY. Um bom exemplo é a Microchip, que providencia toda a informação sobre conformidade de Ethernet em um documento desde o ano passado. Estes são os PHYs que usamos nos nossos módulos, KSZ8041 and KSZ9031. Também compartilho aqui um documento da Texas Instruments, somente como mais um exemplo. Se você está procurando por um novo PHY Ethernet e deseja fazer testes de conformidade, não deixe de pedir ao fabricante informações detalhadas sobre as configurações dos registros de antemão!

- http://ww1.microchip.com/downloads/en/AppNotes/AN2686-Ethernet-Compliance-Test-10BASET-100BASETX-1000BASET.pdf

- http://www.ti.com/lit/an/snla239a/snla239a.pdf

Como visto nas figuras acima, é necessario medir na ordem de picossegundos com precisão. Para isso, precisamos de ferramentas muito boas. Você deve usra um osciloscópio com largura de banda de 1 GHz e memória de 4MS ou mais. Geralmente você precisará de uma estrutura de teste que leva os sinais do jack de Ethernet para as entradas do osciloscópio. É por isso que trabalhamos de perto com a Teledyne LeCroy. Nós temos uma forte colaboração a nível técnico. Usamos um osciloscópio de alta qualidade da série WaveMaster com as ferramentas de hardware e software adequadas. É claro que também há equipamento de outras fabricantes, como Tektronix, Rhode&Schwarz, Keysight e outras.

“A Teledyne LeCroy é líder na fabricação de osciloscópios digitais (DSO). Com DSOs modernos é possível realizar medidas para qualificação. A Toradex usa os equipamentos mais indicados da Teledyne LeCroy para testar o projeto dos PHYs de Ethernet. Combinando o nosso software QualiPHY e os osciloscópios mais recentes, implementou-se um teste semi-automático para testar os níveis físicos dos PHYs de Ethernet de acordo com a especificação IEEE 802.3. Essa solução de medição permite que os engenheiros de desenvolvimento da Toradex testem e resolvam problemas de integridade de sinal o mais cedo possível no projeto dos seus sistemas embarcados. A Toradex se preocupa em usar os equipamentos de medição da forma mais eficiente possível. Se há alguma incerteza ou desvio nas medições, nós trabalhamos juntos para rapidamente resolver esses problemas e fornecer nossa expertise em aplicações de medição.”

Gregor Hofferbert, Teledyne LeCroy

Após realizar um teste de conformidade, nós podemos criar um relatório de conformidade para verificar o projeto da nossa PCI (placa de circuito impresso). Como você pode observar no relatório de teste da Teledyne LeCroy, o Colibri iMX6ULL com a Iris Carrier Board esetão em conformidade com os padrões 10Base-T e 100Base-TX. Assim, temos certeza que nossa implementação funcionará com outros sistemas compatíveis. Por isso, temos a confiança de compartilhar a implementação de Ethernet nas nossas placas com nossos clientes. Você pode encontrar nossos Guias de Projeto de Placas Base aqui: https://developer.toradex.com/carrier-board-design

Nós também compartilhamos todos os projetos de Altium das nossas placas base gratuitamente para nossos clientes. Também fornecemos suporte através de nossa comunidade: https://www.toradex.com/community

Nós começamos a implementar e fornecer nossos softwares de teste na nossa BSP mais recente. Nós adotamos os drtivers já existentes que rodam facilmente nos nossos módulos para fazer os testes de conformidade. Mas, novamente, tenha cuidado: para cada PHY você precisará de técnicas de software diferentes para obter os padrões de teste. Não há receita de bolo. Por exemplo: https://git.toradex.com/cgit/linux-toradex.git/commit/?h=tegra-next&id=13bd0f089ac6babeb7248fe3db4b9c19233cce3c

Note que problemas podem acontecer com erros no roteamento, mau projeto de planos de terra ou imprecisão nos circuitos do cristal. Tudo também depende do ambiente de teste. Loops de terra e fontes ruidosas ou subdimensionadas podem causar erros de medição. É importante seguir os guias de projeto dos fabricantes de PHY. Eu gosto do documento de diagnóstico fornecido pela Intel, pode ser um bom recurso para consultar nos primeiros debugs. Há uma visão geral básica das falhas e suas possíveis origens. Projetos com trilhas muito longas, componentes magnéticos de baixa qualidade ou uso incorreto dos equipamentos de medição sempre podem ser motivo de falha em testes de conformidade. Mas há também erros específicos que têm grande correlação. Por exemplo, valores errados de amplitude são frequentemente causados por resistores de polarização montados incorretamente ou problemas com circuitos de tap central. Bem como valores de jitter altos podem ser causados por problemas no cristal, descasamento de impedância ou fonte de alimentação ruim. No geral, o fabricante do seu PHY deve conseguir lhe ajudar, geralmente até com uma revisão de esquemático ou layout. https://www.intel.com/content/dam/www/public/us/en/documents/application-notes/ieee-conformance-phy-app-note.pdf

Nesse blog, comentei um pouco sobre uma das várias verificações que a Toradex realiza para fornecer produtos de alta qualidade. Nossos testes internos e sua adequação aos nossos guias de projeto reduzem o risco ao mínimo. Para a melhor qualidade possível, você pode fazer a verificação com a sua própria placa base customizada, seguindo os princípios de engenharia de sistemas (como documentado pela NASA, por exemplo), que recomenda realizar testes logo nos primeiros estágios para reduzir riscos e custos. Espero ter contribuido com bastante conteúdo para que você possa se introduzir no assunto. Se você precisar de mais informação, não deixe de entrar em contato.